# Ada User Journal

Volume 45

Number 3

September 2024

Editorial

Quarterly News Digest

Conference Calendar

Forthcoming Events

131

132

146

154

156

157

159

161

162

164

168

171

173

175

## Article

R. Krishnan, A. Gupta, N. Chandrachoodan, V. R. Lalithambika

*Formal Verification of Safety Critical Software in Ada: Two Approaches*

178

---

## Editor in Chief

**António Casimiro**

University of Lisbon, Portugal

*AUJ\_Editor@Ada-Europe.org*

---

## Ada User Journal Editorial Board

**Luís Miguel Pinho**

*Associate Editor*

Polytechnic Institute of Porto, Portugal

*lmp@isep.ipp.pt*

**Jorge Real**

*Deputy Editor*

Universitat Politècnica de València, Spain

*jorge@disca.upv.es*

**Patricia López Martínez**

*Assistant Editor*

Universidad de Cantabria, Spain

*lopezpa@unican.es*

**Dirk Craeynest**

*Events Editor*

KU Leuven, Belgium

*Dirk.Craeynest@cs.kuleuven.be*

**Alejandro R. Mosteo**

*News Editor*

Centro Universitario de la Defensa, Zaragoza, Spain

*amosteo@unizar.es*

---

## Ada-Europe Board

**Luís Miguel Pinho** (President)

Portugal

Polytechnic Institute of Porto

**Dirk Craeynest** (Vice-President)

Belgium

Ada-Belgium & KU Leuven

**Dene Brown** (General Secretary)

United Kingdom

SysAda Limited

**Ahlan Marriott** (Treasurer)

Switzerland

White Elephant GmbH

**António Casimiro** (Ada User Journal)

Portugal

University of Lisbon

---

## Ada-Europe General Secretary

Dene Brown

Tel: +44 2891 520 560

SysAda Limited

Email: [Secretary@Ada-Europe.org](mailto:Secretary@Ada-Europe.org)

Signal Business Center

URL: [www.ada-europe.org](http://www.ada-europe.org)

2 Innotec Drive

BT19 7PD Bangor

Northern Ireland, UK

---

## Information on Subscriptions and Advertisements

Ada User Journal (ISSN 1381-6551) is published in one volume of four issues. The Journal is provided free of charge to members of Ada-Europe. Library subscription details can be obtained direct from the Ada-Europe General Secretary (contact details above). Claims for missing issues will be honoured free of charge, if made within three months of the publication date for the issues. Mail order, subscription information and enquiries to the Ada-Europe General Secretary.

For details of advertisement rates please contact the Ada-Europe General Secretary (contact details above).

---

# ADA USER JOURNAL

Volume 45

Number 3

September 2024

---

## Contents

|                                                                                                                                          | <i>Page</i>       |

|------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Editorial Policy for Ada User Journal                                                                                                    | 130               |

| Editorial                                                                                                                                | 131               |

| Quarterly News Digest                                                                                                                    | 132               |

| Conference Calendar                                                                                                                      | 146               |

| Forthcoming Events                                                                                                                       | 154               |

| Articles from the AEiC 2024 Ada Developers Workshop                                                                                      |                   |

| F. Oleo Blanco, D. Craeynest<br>“First Ada Developers Workshop at AEiC 2024”                                                             | 156               |

| G. Galeotti<br>“SweetAda: a Lightweight Ada-Based Framework”                                                                             | 157               |

| J. R. Carter<br>“Avoiding Access Types”                                                                                                  | 159               |

| G. A. Hazebrouk<br>“G-NAV: Soaring the Clouds with AdaWebPack”                                                                           | 161               |

| A. R. Mosteo<br>“Alire 2.0: a ‘Quality of Life’ Update”                                                                                  | 162               |

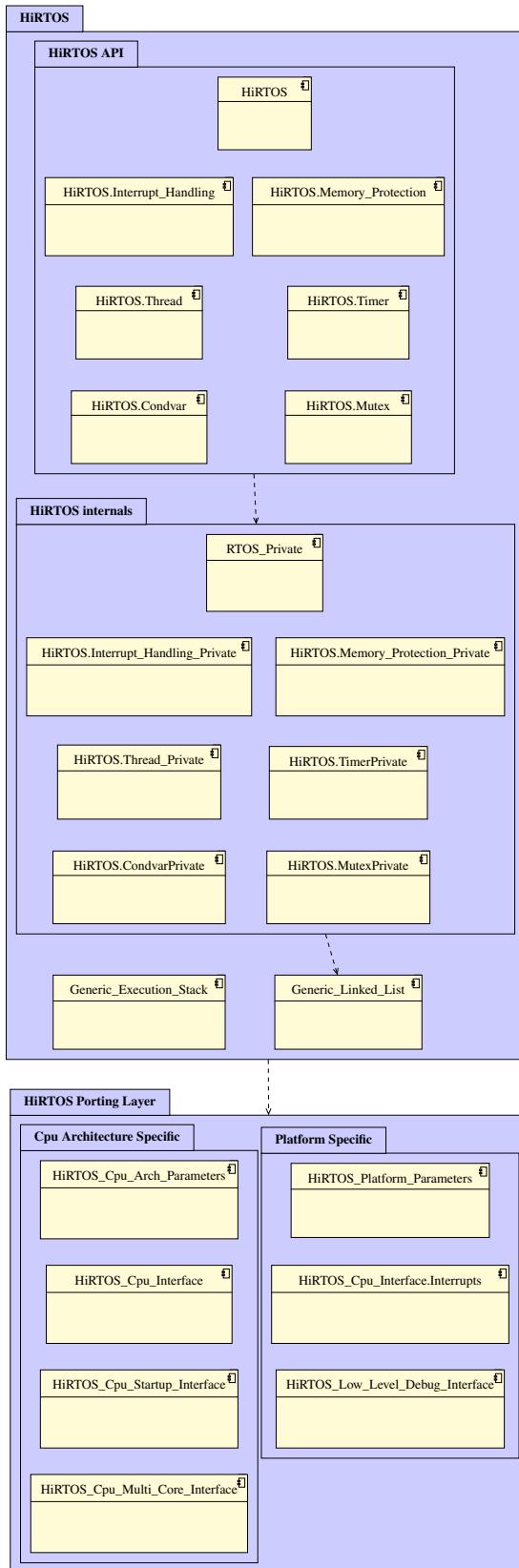

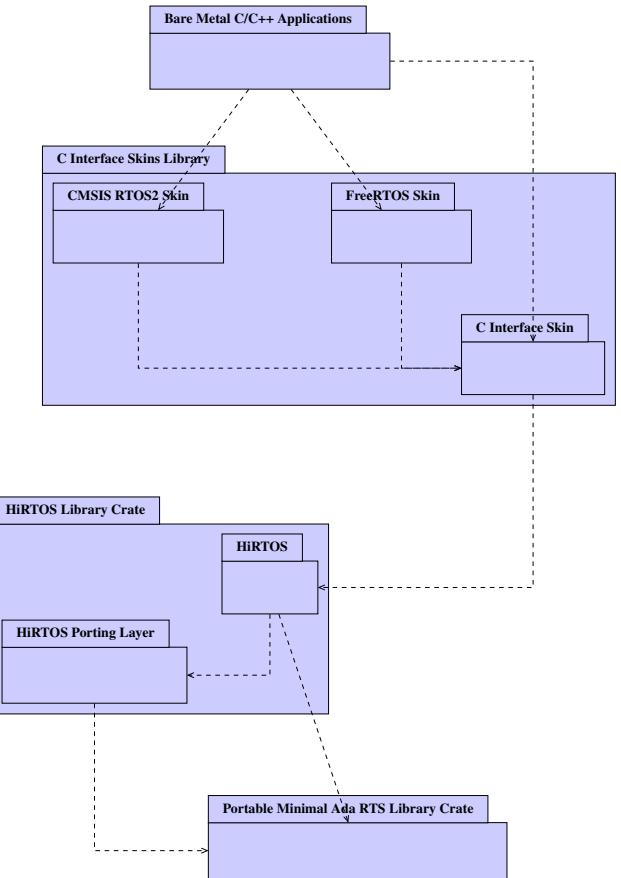

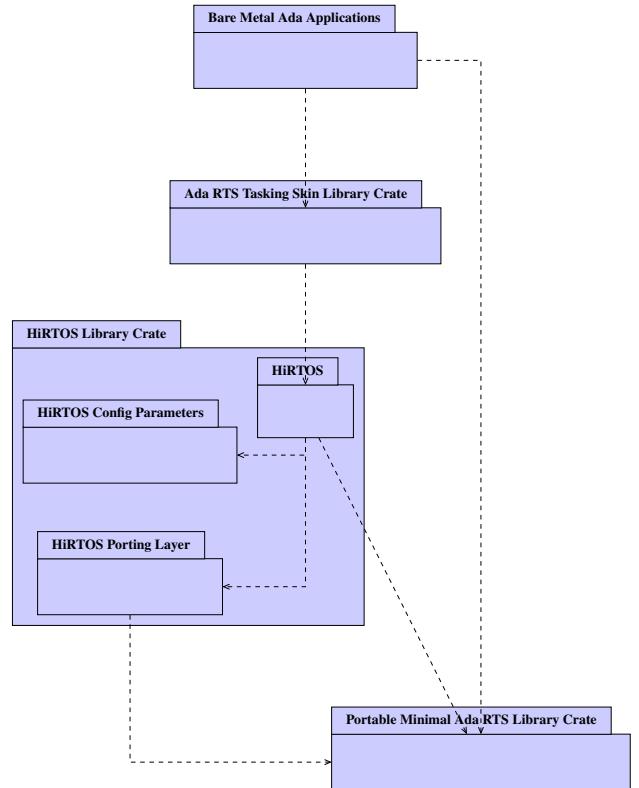

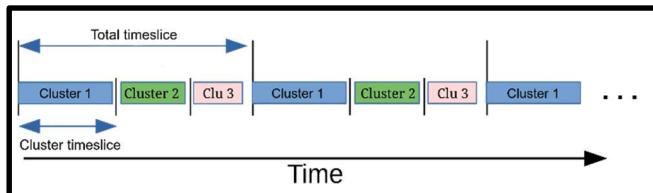

| J. G. Rivera<br>“HiRTOS: A Multi-core RTOS Written in SPARK Ada”                                                                         | 164               |

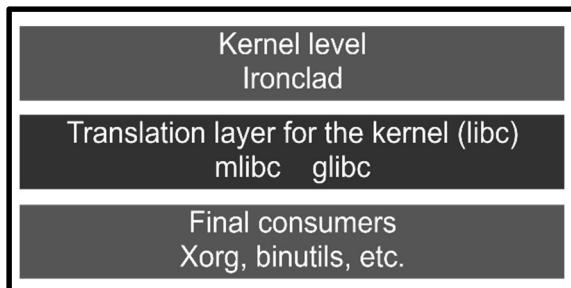

| C. Simon<br>“Ironclad: A Formally Verified OS Kernel Written in SPARK/Ada”                                                               | 168               |

| J. P. Rosen<br>“An Ada Story of Time”                                                                                                    | 171               |

| J. R. Carter<br>“Controlled I/O: a Library for Scope-Based Files”                                                                        | 173               |

| F. Oleo Blanco<br>“Ada Community Advocacy”                                                                                               | 175               |

| Article                                                                                                                                  |                   |

| R. Krishnan, A. Gupta, N. Chandrachoodan, V. R. Lalithambika<br>“Formal Verification of Safety Critical Software in Ada: Two Approaches” | 178               |

| Ada-Europe Associate Members (National Ada Organizations)                                                                                | 194               |

| Ada-Europe Sponsors                                                                                                                      | Inside Back Cover |

# Editorial Policy for Ada User Journal

## Publication

*Ada User Journal* — The Journal for the international Ada Community — is published by Ada-Europe. It appears four times a year, on the last days of March, June, September and December. Copy date is the last day of the month of publication.

## Aims

*Ada User Journal* aims to inform readers of developments in the Ada programming language and its use, general Ada-related software engineering issues and Ada-related activities. The language of the journal is English.

Although the title of the Journal refers to the Ada language, related topics, such as reliable software technologies, are welcome. More information on the scope of the Journal is available on its website at [www.ada-europe.org/auj](http://www.ada-europe.org/auj).

The Journal publishes the following types of material:

- Refereed original articles on technical matters concerning Ada and related topics.

- Invited papers on Ada and the Ada standardization process.

- Proceedings of workshops and panels on topics relevant to the Journal.

- Reprints of articles published elsewhere that deserve a wider audience.

- News and miscellany of interest to the Ada community.

- Commentaries on matters relating to Ada and software engineering.

- Announcements and reports of conferences and workshops.

- Announcements regarding standards concerning Ada.

- Reviews of publications in the field of software engineering.

Further details on our approach to these are given below. More complete information is available in the website at [www.ada-europe.org/auj](http://www.ada-europe.org/auj).

## Original Papers

Manuscripts should be submitted in accordance with the submission guidelines (below).

All original technical contributions are submitted to refereeing by at least two people. Names of referees will be kept confidential, but their comments will be relayed to the authors at the discretion of the Editor.

The first named author will receive a complimentary copy of the issue of the Journal in which their paper appears.

By submitting a manuscript, authors grant Ada-Europe an unlimited license to publish (and, if appropriate, republish) it, if and when the article is accepted for publication. We do not require that authors assign copyright to the Journal.

Unless the authors state explicitly otherwise, submission of an article is taken to imply that it represents original, unpublished work, not under consideration for publication elsewhere.

## Proceedings and Special Issues

The *Ada User Journal* is open to consider the publication of proceedings of workshops or panels related to the Journal's aims and scope, as well as Special Issues on relevant topics.

Interested proponents are invited to contact the Editor-in-Chief.

## News and Product Announcements

Ada User Journal is one of the ways in which people find out what is going on in the Ada community. Our readers need not surf the web or news groups to find out what is going on in the Ada world and in the neighbouring and/or competing communities. We will reprint or report on items that may be of interest to them.

## Reprinted Articles

While original material is our first priority, we are willing to reprint (with the permission of the copyright holder) material previously submitted elsewhere if it is appropriate to give it a

wider audience. This includes papers published in North America that are not easily available in Europe.

We have a reciprocal approach in granting permission for other publications to reprint papers originally published in *Ada User Journal*.

## Commentaries

We publish commentaries on Ada and software engineering topics. These may represent the views either of individuals or of organisations. Such articles can be of any length — inclusion is at the discretion of the Editor.

Opinions expressed within the *Ada User Journal* do not necessarily represent the views of the Editor, Ada-Europe or its directors.

## Announcements and Reports

We are happy to publicise and report on events that may be of interest to our readers.

## Reviews

Inclusion of any review in the Journal is at the discretion of the Editor. A reviewer will be selected by the Editor to review any book or other publication sent to us. We are also prepared to print reviews submitted from elsewhere at the discretion of the Editor.

## Submission Guidelines

All material for publication should be sent electronically. Authors are invited to contact the Editor-in-Chief by electronic mail to determine the best format for submission. The language of the journal is English.

Our refereeing process aims to be rapid. Currently, accepted papers submitted electronically are typically published 3-6 months after submission. Items of topical interest will normally appear in the next edition. There is no limitation on the length of papers, though a paper longer than 10,000 words would be regarded as exceptional.

# Editorial

As we welcome you to this September issue of the Ada User Journal, I would like to begin by extending my warmest congratulations to Luís Miguel Pinho, our Associate Editor, on his appointment as President of Ada-Europe. I would also like to express my appreciation for Tullio Vardanega, who, after serving as President of Ada-Europe for so many years, now takes on the leadership of the newly established Ada User Society. Both assume significant responsibilities in shaping the future of the Ada language, and I wish them every success in their new roles. Their dedication and expertise will undoubtedly contribute to ensuring the continuity and, hopefully, the growth of the Ada community.

Regarding the technical content, this issue features the Proceedings of the Ada Developers Workshop, which was co-located with the 28th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2024) last June in Barcelona. The proceedings open with an introductory note by the workshop organizers, Fernando Oleo Blanco and Dirk Craeynest, followed by nine concise articles summarizing the respective presentations at the workshop. These contributions explore various aspects of the Ada language, including language-specific features, related tools, and systems written in Ada, as well as an especially thought-provoking article reflecting on the present and future of Ada. We hope these proceedings will offer valuable insights and perhaps inspire participation in future editions for those who could not attend the workshop—or even for those who did.

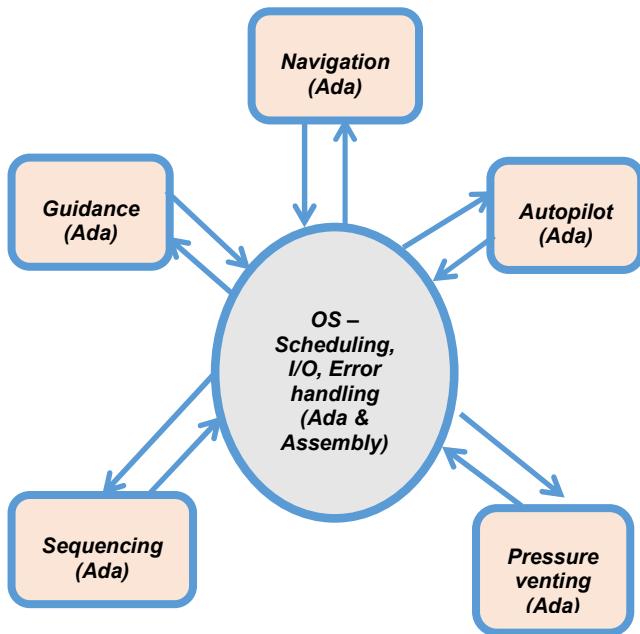

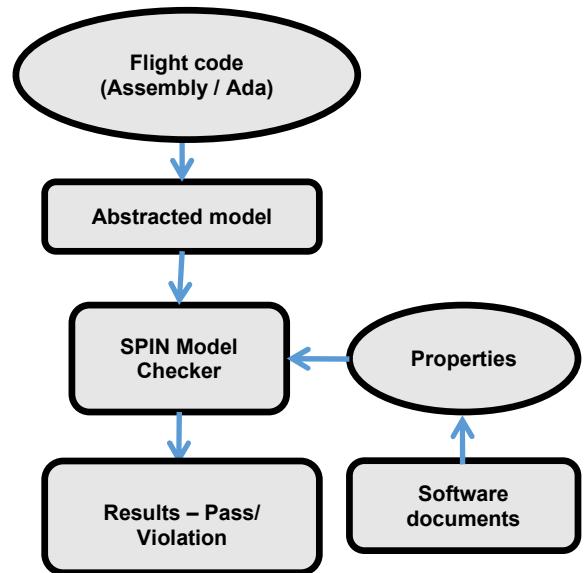

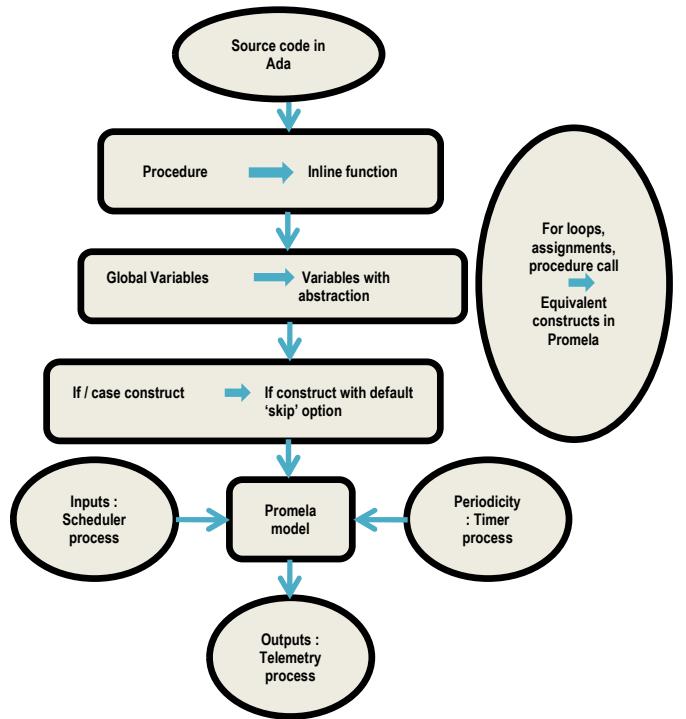

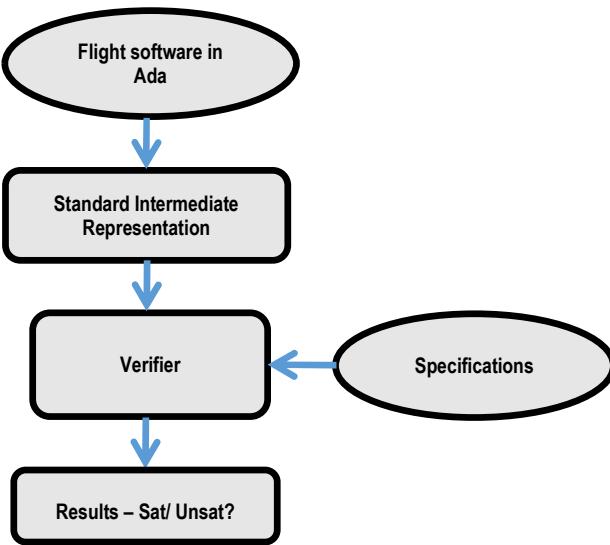

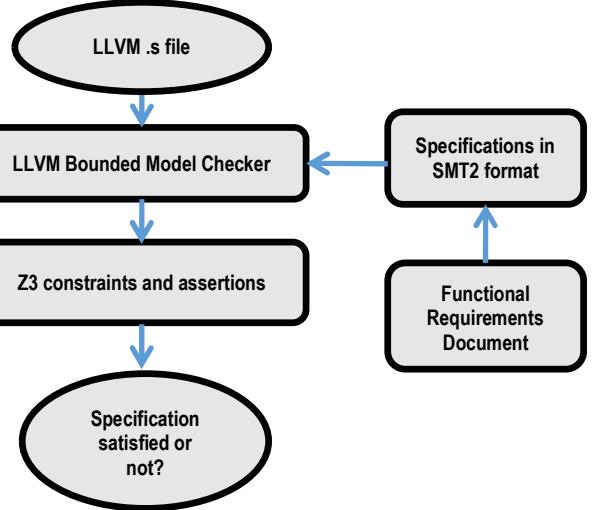

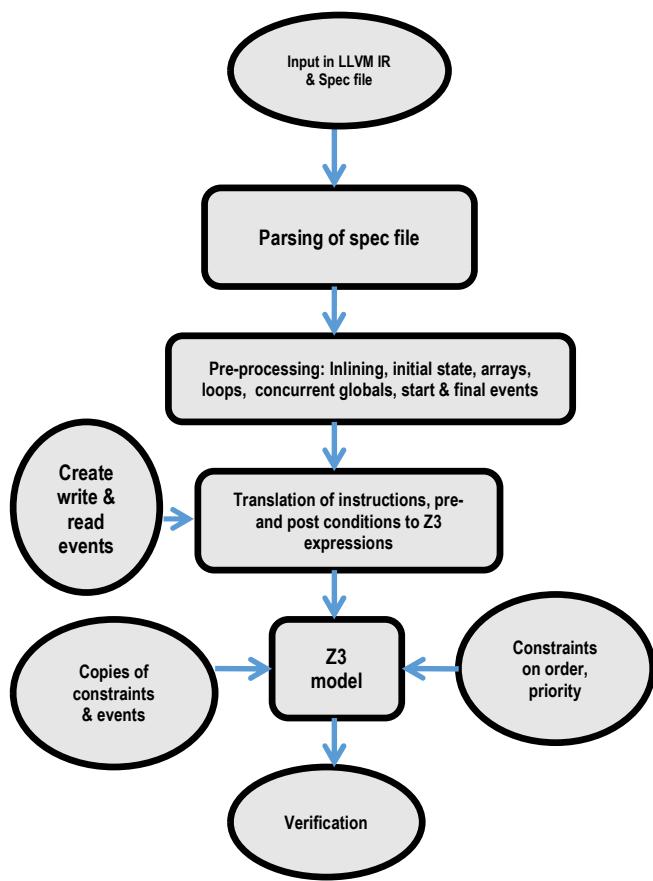

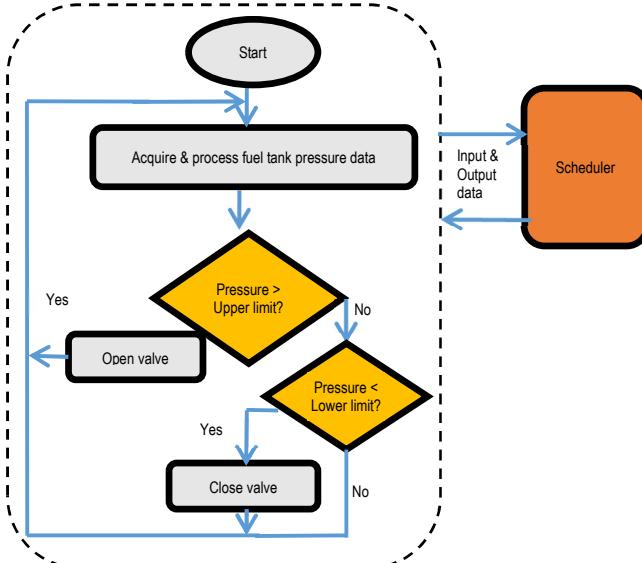

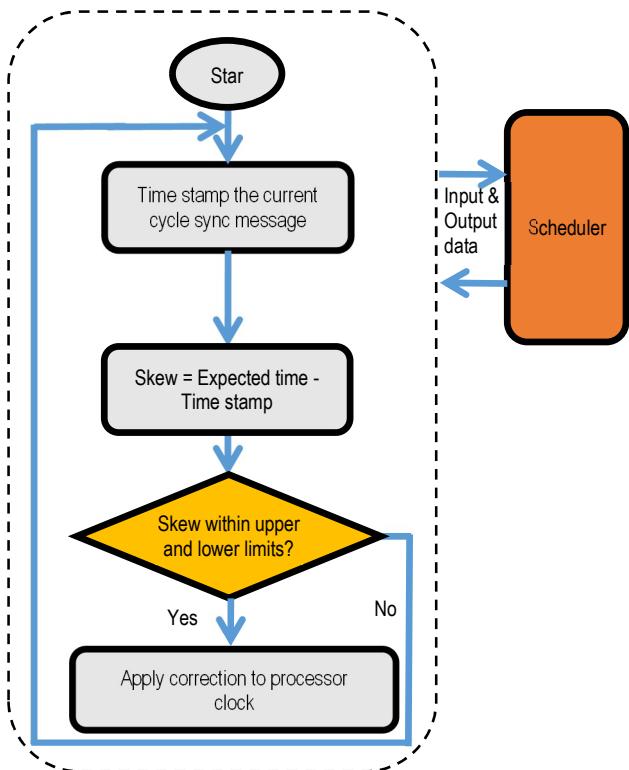

This issue also features a contributed article on the formal verification of safety-critical software written in Ada, authored by a team of researchers from the Vikram Sarabhai Space Centre, IIT Bombay, and IIT Madras in India. The article explores the use of the SPIN model checker, combined with a custom toolchain, to perform static analysis of Ada code and help ensuring software reliability in critical applications.

As always, we include our News Digest and Calendar sections, expertly curated by their respective editors, Alejandro R. Mosteo and Dirk Craeynest. Following the calendar, readers will find the Call for Papers for the 29th Ada-Europe International Conference on Reliable Software Technologies (AEiC 2025), set to take place from June 10–13, 2025, in Paris, France. With multiple tracks and submission formats available, we encourage everyone to contribute and be part of this exciting event!

*Antonio Casimiro

Lisboa

September 2024

Email: AUJ\_Editor@Ada-Europe.org*

# Quarterly News Digest

Alejandro R. Mosteo

Centro Universitario de la Defensa de Zaragoza, 50090, Zaragoza, Spain; Instituto de Investigación en Ingeniería de Aragón, Mariano Esquillor s/n, 50018, Zaragoza, Spain; email: amosteo@unizar.es

## Contents

|                            |     |

|----------------------------|-----|

| Preface by the News Editor | 132 |

| Ada-related Events         | 132 |

| Ada-related Resources      | 133 |

| Ada-related Tools          | 136 |

| Ada Inside                 | 137 |

| Ada and Other Languages    | 138 |

| Ada Practice               | 138 |

[Messages without subject/newsgroups are replies from the same thread. Messages may have been edited for minor proofreading fixes. Quotations are trimmed where deemed too broad. Sender's signatures are omitted as a general rule. —arm]

## Preface by the News Editor

Dear Reader,

Today, I want to highlight two conversations in the Digest that interested me particularly. Firstly, documentation about the 'Red' language has been found online, and it seems that this completes the availability of all contestants from which Ada emerged victorious [1]. Curiously, I found the style of the code not that unfamiliar for an Ada programmer.

Secondly, an animated discussion emerged around the idea of "what Jean Ichbiah would want to find in Ada 2022" [2]. Therein you can also find the reservations he had about preliminary versions of Ada 95 [3], which is in itself worth a read if you have not read them before (as I had not).

Sincerely,

Alejandro R. Mosteo.

[1] "Red" and the DoD Language Competition", in Ada and Other Languages.

[2] "Ichbiah 2022 Compiler Mode", in Ada Practice

[3] <https://web.elastic.org/~fche/mirrors/old-usenet/ada-with-null>

## Ada-related Events

### [AEiC 2024] Ada Developers Workshop Videos and Slides

*From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz>*

*Subject: [AEiC 2024] Ada Developers Workshop videos and slides are public*

*Date: Thu, 8 Aug 2024 20:49:18 +0200*

*Newsgroups: comp.lang.ada*

Dear Ada community,

the recordings of the talks that were held in the Ada Developers Workshop have been made available in the AEiC 2024 website [1]. The slides for each presentation can also be found there. The links can be found just under the title for each entry.

Also, huge thanks to Dirk, Nam, Fabien, the organisers of the conference; Ada-Europe and AdaCore for their sponsorship and their funding to get the technology ready to record the Workshop.

[1] <https://www.ada-europe.org/conference2024/adadev.html>

Best regards,

Fer & the Ada Developers Workshop team

P.S: any kind of feedback is more than welcome!

### Ada Monthly Meetup, September 2024

*From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz>*

*Subject: Ada Monthly Meetup, September 2024*

*Date: Sun, 11 Aug 2024 17:21:09 +0200*

*Newsgroups: comp.lang.ada*

I would like to announce the September (2024) Ada Monthly Meetup which will be taking place on the 7th of September at 13:00 UTC time (15:00 CEST). As always the meetup will take place over at Jitsi. The Meetup will also be livestreamed/recoded to YouTube.

If someone would like to propose a talk or a topic, feel free to do so! We currently have no proposals. Nonetheless, I would like to talk about the AEiC 2024 Ada Developers Workshop, remind people about the 2024 Crate of the Year Award

and maybe talk a bit about the Ada Users Society :)

Here are the connection details from previous posts: The meetup will take place over at Jitsi, a conferencing software that runs on any modern browser. The link is Jitsi Meet The room name is "AdaMonthlyMeetup" and in case it asks for a password, it will be set to "AdaRules". I do not want to set up a password, but in case it is needed, it will be the one above without the quotes. The room name is generally not needed as the link should take you directly there, but I want to write it down just in case someone needs it.

### Ada Monthly Meetup, 5th October 2024

*From: Fernando Oleo / Irvise <irvise\_ml@irvise.xyz>*

*Subject: Ada Monthly Meetup, 5th October 2024*

*Date: Mon, 16 Sep 2024 22:43:14 +0200*

*Newsgroups: comp.lang.ada*

I would like to announce the October (2024) Ada Monthly Meetup which will be taking place on the \*\*5th of October at 13:00 UTC time (15:00 CEST).\*\* As always the meetup will take place over at Jitsi. The Meetup will also be livestreamed/recoded to YouTube.

\*\*If someone would like to propose a talk or a topic, feel free to do so! We currently have no proposals.\*\* Nonetheless, I would like to bring some topics that were left off during September's Meetup.

Here are the connection details from previous posts: The meetup will take place over at Jitsi [1], a conferencing software that runs on any modern browser. The link is Jitsi Meet The room name is "AdaMonthlyMeetup" and in case it asks for a password, it will be set to "AdaRules". I do not want to set up a password, but in case it is needed, it will be the one above without the quotes. The room name is generally not needed as the link should take you directly there, but I want to write it down just in case someone needs it.

Best regards and see you soon!

Fer

[1] <https://meet.jit.si/AdaMonthlyMeetup>

P.S: you can see the September summary in <https://forum.ada-lang.io/t/ada-monthly-meeting-september-2024/1073/6> or in YouTube (with audio issues) [https://www.youtube.com/live/i\\_bVoiDlw5E](https://www.youtube.com/live/i_bVoiDlw5E)

## Ada-related Resources

[Delta counts are from July 11th to November 13th. —arm]

### Ada on Social Media

*From: Alejandro R. Mosteo <amosteo@unizar.es>*

*Subject: Ada on Social Media*

*Date: 13 Nov 2024 19:35 CET [b]*

*To: Ada User Journal readership*

Ada groups on various social media:

- Reddit: 8\_868 (+127) members [1]

- LinkedIn: 3\_549 (+28) members [2]

- Stack Overflow: 2\_426 (+15) questions [3]

- Ada-lang.io: 287 (+46) users [4]

- Gitter: 271 (+13) people [5]

- Telegram: 208 (+3) users [6]

- Libera.Chat: 69 (-4) concurrent users [7]

[1] <https://old.reddit.com/r/ada/>

[2] <https://www.linkedin.com/groups/114211/>

[3] <https://stackoverflow.com/questions/tagged/ada>

[4] <https://forum.ada-lang.io/u>

[5] [https://app.gitter.im/#/room/#ada-lang\\_Lobby:gitter.im](https://app.gitter.im/#/room/#ada-lang_Lobby:gitter.im)

[6] [https://t.me/ada\\_lang](https://t.me/ada_lang)

[7] <https://netsplit.de/channels/details.php?room=%23ada&net=Libera.Chat>

### Repositories of Open Source Software

*From: Alejandro R. Mosteo <amosteo@unizar.es>*

*Subject: Repositories of Open Source software*

*Date: 13 Nov 2024 19:39 CET [c]*

*To: Ada User Journal readership*

GitHub: >1\_000\* (+260) developers [1]

Rosetta Code: 1\_005 (+26) examples [2]

42 (=) developers [3]

Alire: 483 (+71) crates [4]

1\_268 (+200) releases [5]

Sourceforge: 251 (-1) projects [6]

Open Hub: 214 (=) projects [7]

Codelabs: 60 (+3) repositories [8]

Bitbucket: 37 (=) repositories [9]

\*This number is a lower bound due to GitHub search limitations.

[1] <https://github.com/search?q=language%3AAda&type=Users>

[2] <https://rosettacode.org/wiki/Category:Ada>

[3] [https://rosettacode.org/wiki/Category:Ada\\_User](https://rosettacode.org/wiki/Category:Ada_User)

[4] <https://alire.ada.dev/crates.html>

[5] `alr search --list --full`

[6] <https://sourceforge.net/directory/language:ada/>

[7] <https://www.openhub.net/tags?names=ada>

[8] [https://git.codelabs.ch/?a=project\\_index](https://git.codelabs.ch/?a=project_index)

[9] <https://bitbucket.org/repo/all?name=ada&language=ada>

### Language Popularity Rankings

*From: Alejandro R. Mosteo <amosteo@unizar.es>*

*Subject: Ada in language popularity rankings*

*Date: 13 Nov 2024 19:48 CET*

*To: Ada User Journal readership*

[Positive ranking changes mean to go up in the ranking. —arm]

- TIOBE Index: 25 (-1) 0.71% (-0.08%) [1]

- PYPL Index: 15 (+2) 1.03% (+0.07%) [2]

- Languish Trends: 153 (+39) 0.01% (+0.01%) [3]

- Stack Overflow Survey: 40 (+2) 0.9% (+0.13%) [4]

- IEEE Spectrum (general): 50 (-14) Score: 0.0014 0107 (-0.093) [5]

- IEEE Spectrum (jobs): 55 (-26) Score: 0.0 (-0.0173) [5]

- IEEE Spectrum (trending): 46 (-16) Score: 0.0022 (0.01) [5]

[1] <https://www.tiobe.com/tiobe-index/>

[2] <http://pypl.github.io/PYPL.html>

[3] <https://tjpalmer.github.io/languish/>

[4] <https://survey.stackoverflow.co/2024/>

[5] <https://spectrum.ieee.org/top-programming-languages/>

### Re: Ada-Lang and Its Forum

*From: Randy Brukardt <randy@rrsoftware.com>*

*Subject: Re: Ada-Lang and it's (more active than CLA) forum*

*Date: Tue, 2 Jul 2024 02:55:49 -0500*

*Newsgroups: comp.lang.ada*

[Cont'd from AUJ 45-2, April 2024

—arm]

> Ada-Lang is a community maintained and supported webpage whose intent is to give a nice "landing page" to anybody wanting to learn Ada and become a hub for all Ada users.

I was adding this site to AdaIC's "Learn" pages (I think it disappeared some years ago, it is good to see it back), and noted that nowhere does it identify itself as "Ada-Lang" or any other short name on the site itself. It just calls itself "Ada Programming Language", which is a bit grandiose (there are a number of sites that can lay claim to part of that title, but surely none that can lay claim to all of it). Within the Ada Community in particular, it helps to identify the site more precisely. And I don't think that many people really look at the links that they click on, I doubt many people using AdaIC do, so just using the domain name and assuming people know what it is without any identification elsewhere is not ideal.

My two cents worth. (Humm, given prices these days, I don't think you can actually buy anything with two cents. That's probably one cliche that needs updating. ;-)

### AWS-friendly Web Hosting

*From: Marius Alves <marius2023pt@gmail.com>*

*Subject: Ada/GNAT/AWS-friendly web hosting*

*Date: Thu, 12 Sep 2024 15:25:41 +0100*

*Newsgroups: comp.lang.ada*

Researching how to build an HTTP server (serving a website) on a local machine (MacOS) using AWS (Ada Web Server) and deploy it on a web hosting provider (e.g. 1dollar-webhosting.com).

Anyone done that? I've searched but could not find [anything].

Thanks.

Some specific questions on my mind follow.

Is a macOS host required (e.g. Ultahost 15 euros/month; I'd rather stay with 1dollar)?

If the host runs on Linux then cross-building (from macOS to Linux) is required, right? GNAT does that, right?

Or, must the program be built in the host? (Thus requiring GNAT to be there.)

The host is already running an HTTP server program (probably Apache). Must it be turned off? How?

In general, can the executable be launched on a VPS (Virtual Private Server)? Which port?

Will dynamic linking work? I'm guessing not, so, static; but then, will GNAT integrate the right libraries for Linux in the executable?

Will "Community GNAT" do? (Instead of GNAT Pro.)

Are those the right questions?

Thanks, thanks, thanks, thanks, thanks, thanks and thanks.

*From: J-P. Rosen <rosen@adalog.fr>*

*Date: Thu, 12 Sep 2024 16:48:40 +0200*

Adalog's site (<https://www.adalog.fr/>) is a standalone program written in Ada with AWS.

So are the sites for the various Ada-Europe conferences (see <https://www.adaeurope.org/conference2024/> for example).

And many others...

> Is a macOS host required

No

> If the host runs on Linux then cross-building (from macOS to Linux) required, right?

Never tried, but no reason it shouldn't be possible

> Or, must the program be built in the host?

That's what I do

> The host is already running an HTTP server program (probably Apache). Must it be turned off? How?

Of course, you cannot have two programs listening on the same port, so if you want to listen to 80 or 8080, you'd better stop Apache (or any other program) to do that. As for me, I don't run Apache at all.

> In general, can the executable be launched on a VPS (Virtual Private Server)? Which port?

The port is given by the initial data of AWS

> Will dynamic linking work?

You just compile your program like any other Ada program

> Will "Community GNAT" do? (Instead of GNAT Pro.)

Yes, that's what I do

> Are those the right questions?

All questions are right....

> Thanks, thanks, thanks, thanks, thanks, thanks and thanks.

You're welcome

*From: Drpi <314@drpi.fr>*

*Date: Thu, 12 Sep 2024 16:54:45 +0200*

> The host is already running an HTTP server program (probably Apache). Must it be turned off? How?

The usual way is to use Apache (or nginx or another one) as a front end. Your application uses port 1080 (or something else) and the front end relays this port to the external 80 port.

This way, the security stuff is managed by the front end, not your application. You can also run multiple applications, each being redirected to its domain name/path.

*From: Jeffrey R. Carter <spam.jrcarter.not@spam.acm.org.not>*

*Date: Thu, 12 Sep 2024 18:22:28 +0200*

> Researching how to build an HTTP server (serving a website) on a local machine (MacOS) using AWS (Ada Web Server) and deploy it on a web hosting provider (e.g. 1dollar-webhosting.com).

In my experience, this would be easier done with Gnoga (<https://sourceforge.net/projects/gnoga/>) than AWS. On a web-based system using AWS quite a while ago, we had to have a number of JS files. Although we had a lot more Ada than JS, we spent a lot more effort correcting JS errors than Ada errors.

Gautier de Montmollin has made Gnoga programs publicly available, such as his Pasta! game (<http://pasta.phyrama.com/>), so might be able to help with your hosting questions.

*From: J-P. Rosen <rosen@adalog.fr>*

*Date: Thu, 12 Sep 2024 19:06:08 +0200*

> This way, the security stuff is managed by the front end

But security breaches mainly use known bugs in Apache... If you write your own server with AWS, the attacker knows nothing about the software that answers! And as for buffer overflow attacks... Well, it's Ada. You'll see some handled Constraint\_Error in the log file, end of story!

*From: Kevin Chadwick <kc-usenet@chadwicks.me.uk>*

*Date: Thu, 12 Sep 2024 17:16:29 -0000*

> But security breaches mainly use known bugs in Apache... [...]

AWS uses OpenSSL or a fair bit better LibreSSL for TLS, written in C and quite often found vulnerable. You could isolate the nginx proxy to another machine though.

*From: Dmitry A. Kazakov <mailbox@dmitry-kazakov.de>*

*Date: Thu, 12 Sep 2024 20:48:29 +0200*

> Researching how to build an HTTP server (serving a website) on a local machine (MacOS) using AWS (Ada Web Server) and deploy it on a web hosting provider (e.g. 1dollar-webhosting.com).

That depends on what the provider would allow you to upload to the host. Likely nothing executable... (-:)

> If the host runs on Linux then cross-building (from macOS to Linux) is required, right?

It is possible, but far simpler would be a virtual machine running Linux. E.g. I compile for Linux targets on virtual machines. Only for ARM I am using physical machines. You must know what kind of Linux your provider has in order to choose the right version of the libc etc. [...]

> Will dynamic linking work?

If you ship the libraries together with the server. Then if the host runs Apache it must have some TLS library installed. You must learn the version and link against it. In any case you need either OpenSSL or else GNUTLS. The HTTP server from Simple Components can use both. I believe that either can be built as a static library. I see no reason why AWS could not be linked statically. BTW you must maintain certificates on the server.

> Will "Community GNAT" do?

I am not sure if all-static builds were possible, e.g. libc, libgnat.

*From: Lawrence D'Oliveiro <ldo@nz.invalid>*

*Date: Thu, 12 Sep 2024 22:29:36 -0000*

> we spent a lot more effort correcting JS errors than Ada errors.

Did you "use strict"?

*From: Jeffrey R. Carter <spam.jrcarter.not@spam.acm.org.not>*

*Date: Fri, 13 Sep 2024 11:03:03 +0200*

> Did you "use strict"?

I don't know. It was quite a while ago and I didn't work on the JS. But the point is that when you use Gnoga, you don't need any to create any JS.

*From: Lawrence D'Oliveiro <ldo@nz.invalid>*

*Date: Thu, 12 Sep 2024 22:35:20 -0000*

> But security breaches mainly use known bugs in Apache...

That's called "security through obscurity". Not recommended.

*From: Lawrence D'Oliveiro <ldo@nz.invalid>*

*Date: Thu, 12 Sep 2024 22:40:35 -0000*

> The usual way is to use Apache (or nginx or another one) as a front end.

Yup, I do things this way for my Python+ASGI code, too. This is called a "reverse proxy", though I don't know why -- I think "server-side proxy" would be more accurate.

Make sure your back-end server is listening only on a loopback address: 127.0.0.0/8 (IPv4) or ::1 (IPv6). That way the only access to it from outside the machine is through the public web-server front end.

(Question to ponder: why does IPv4 offer over 16 million different loopback addresses, while IPv6, with its much larger address space, has to make do with only one?)

*From: J-P. Rosen <rosen@adalog.fr>

Date: Fri, 13 Sep 2024 08:46:33 +0200*

> That's called "security through obscurity". Not recommended.

No, AWS is public and there is nothing hidden. Just that, since there are wayyyyy more users of Apache than of AWS, attackers will not bother to try to break in

*From: Stéphane Rivière

<stef@genesix.org>

Date: Fri, 13 Sep 2024 15:15:03 +0200*

As a professional web hoster, I strongly advise you to forget Apache and use only Nginx, both as a proxy (in your case) and as a web server (generic case). Not only does Apache have security problems, but its performance is pitiful compared to Nginx.

If you have several sites, the ideal solution is to enter everything in https/port 443 on the nginx proxy (which will be able to manage X509/TLS https certificates) and exit on as many ports 8080, 8081, 8082, etc. as you have websites.

*From: Björn Persson

<bjorn@xn--rombobjrn-67a.se>

Date: Fri, 13 Sep 2024 16:33:15 +0200*

> Researching how to build an HTTP server (serving a website) on a local machine (MacOS) using AWS (Ada Web Server) and deploy it on a web hosting provider (e.g. 1dollar-webhosting.com).

I don't know about 1dollar, but a typical web hosting provider will only let you upload static files (HTML, pictures et cetera), limited snippets of web server configuration, and certain kinds of programs that run under their web server's control. PHP is common. Some might run Perl programs with mod\_perl, or Python programs using WSGI.

Maybe some web hosts support CGI or FastCGI. Those interfaces can be implemented in Ada. I think you'll have limited use for AWS in that case, as the HTTP parsing is handled by the web server.

I think it would be hard to find a web host that lets you run arbitrary network-facing daemons. To run your own web server you want a VPS (or a physical server in a colocation facility, but if your security needs don't rule out a web host, then a VPS is also fine).

> The host is already running an HTTP server program (probably Apache). Must it be turned off? How?

A typical web host won't let you turn off their web server. They serve many customers' content from the same Apache instance, so turning that off would break all those websites.

> In general, can the executable be launched on a VPS (Virtual Private Server)?

Sure. In a VPS you have the whole operating system to yourself (maybe except for the kernel if the VPS provider uses OpenVZ). You install and run whatever programs you want, just like on your own physical computer. Maybe you'll be able to get a VPS with macOS, if that's your preference.

In a VPS it's also your responsibility to install updates regularly, and upgrade to a new major OS version from time to time. If you fail to keep up, then criminals will take over your VPS and use it as a relay when attacking others. Make sure that you'll be notified automatically when there are updates to install.

> If the host runs on Linux then cross-building (from macOS to Linux) is required, right?

GCC – and thus GNAT – can be built as a cross-compiler. Perhaps you can find one that someone has built and packaged for MacOS. Otherwise you'll need to build your own from the GCC source code, configuring it to be a cross-compiler. (That's theoretical knowledge. I have no practical experience with cross-compilation).

> Or, must the program be built in the host? (Thus requiring GNAT to be there.)

No, but in my opinion it's much easier that way. Either build on the computer you'll run on, or on another computer of the same processor architecture, running the same version of the same operating system. That way you don't need to worry about getting the wrong version of some library or build tool.

> Will dynamic linking work?

Cross-compilation should be able to work with shared libraries. Regardless of whether the libraries are shared or static, libraries for the target machine must be available on the build host. I guess you would either install packaged libraries on the target machine, and copy those to the build host, or else cross-compile the libraries too. You need to configure search paths carefully so that both the compiler and the linker find the cross-libraries instead of the native ones. This is one of the complications you avoid by building natively.

> Which port?

Normally port 443, because of course you'll use HTTPS, won't you? Optionally you can also have an HTTP server on port

80 that responds to every request with a redirection to HTTPS.

If you choose to put AWS behind a reverse proxy like DrPi suggested, then the reverse proxy listens on port 443 on your public IP address, and you tell AWS to listen on some other port and only on the localhost address, ::1 or 127.0.0.1.

*From: Randy Brukardt

<randy@rrsoftware.com>

Date: Sat, 14 Sep 2024 01:38:16 -0500*

> That's called "security through obscurity". Not recommended.

That's the wrong way to look at it. An Ada program is better thought of as "security by simplicity and correctness", because you are running an Ada that only does a few things (and which can be thoroughly tested, checked with static analysis, and so on) rather than a general program that does a zillion things (with many combinations that can't be tested).

The only place "obscurity" comes into it is that no one else is running the exact same program as you. So attacks that depend on any sort of knowledge of the program cannot succeed.

In any case, there is no such thing as "secure", there are only levels, and for the sorts of non-critical stuff that we're doing, an Ada program is certainly secure enough. I wouldn't try to run a storefront on it (although that would be more because you'd have a hard time convincing your bank that it is OK than any real problems), or anything that needs high-level security.

*From: Kevin Chadwick <kc-usenet@chadwicks.me.uk>

Date: Sat, 14 Sep 2024 12:02:05 -0000*

> work with Gnoga

(<https://v22.soweb.io>).

Runs on Android/IOS. Does that require an internet web server?

*From: Stéphane Rivière

<stef@genesix.org>

Date: Sat, 14 Sep 2024 15:00:00 +0200*

> Runs on Android/IOS.

Yes, v22.Gui/Gnoga is responsive. Tested with 5" smartphones as old as Nexus 5 (with a browser more recent than the stock one to handle websockets). Also tested on 43" 4K ;)

On some iOS devices, the menu bar is slightly offset. I didn't look too hard. It's a Safari problem. It works fine with Firefox and Chrome.

> Does that require an internet web server?

Not necessarily. v22.Gui/Gnoga supports itself X509 TLS https certificates (tested). However, for various reasons (such as the possibility of having several web applications on the same instance and on

the same 80/443 input port), in production, I've always chosen to have a Nginx proxy on the front end, which is also more flexible and handles automatic switching from http/80 to https/443.

## adaic.org; Is There a Problem?

*From: John McCabe

<john@nospam.mccabe.org.uk>

Subject: adaic.org; is there a problem?

Date: Tue, 17 Sep 2024 16:19:47 -0000

Newsgroups: comp.lang.ada*

Sorry to ask here; I wasn't sure where else to go, but is [www.adaic.org](http://www.adaic.org) ok for everyone? I'm just seeing a mostly white screen with a blackish bar at the top on Firefox, Chrome and Edge (Chrome on both Windows and Android). It might just be me, but I thought I'd ask in case anyone else sees it like that and can prod the right people to fix it or, alternatively, just let me know that it's a problem at my end!

*From: Bill Findlay

<findlaybill@blueyonder.co.uk>

Date: Tue, 17 Sep 2024 18:35:16 +0200*

FOOBAR.

It looks as though a significant part of the HTML is missing.

*From: John McCabe

<john@nospam.mccabe.org.uk>

Date: Tue, 17 Sep 2024 16:42:37 -0000*

Thanks for that Bill; at least I'm not going mad then :-)

*From: Dirk Craeynest

<dirk@orka.cs.kuleuven.be>

Date: Tue, 17 Sep 2024 17:59:37 -0000*

I noticed the problem with adaic.org as well, and have informed Randy, its webmaster, yesterday already. Stay tuned until he kicks the server back into action... ;-)

*From: Blady <p.p11@orange.fr>

Date: Mon, 23 Sep 2024 20:31:42 +0200*

I noticed a similar problem with [www.ada-auth.org](http://www.ada-auth.org)?

*From: Luke A. Guest

<laguest@archeia.com>

Date: Tue, 24 Sep 2024 13:56:47 +0100*

Yup both down, just tried them.

## Ada-related Tools

### GNAT Studio 25.0 for macOS Ventura.

*From: Blady <p.p11@orange.fr>

Subject: [ANN] GNAT Studio 25.0 for

macOS Ventura.

Date: Fri, 26 Jul 2024 12:02:15 +0200

Newsgroups: comp.lang.ada*

Here is a very preliminary version of GNAT Studio 25.0wa as a standalone app for macOS:

[https://sourceforge.net/projects/gnuada/files/GNAT\\_GPL\\_Mac\\_OS\\_X/2024-ventura](https://sourceforge.net/projects/gnuada/files/GNAT_GPL_Mac_OS_X/2024-ventura)

NEW:

The GNATStudio launcher looks for a gnatstudio\_launcher.rc file in the .gnatstudio folder from either \$HOME or \$GNATSTUDIO\_HOME locations. If it exists, we can define some environment variables with the standard syntax VAR=VALUE. If the VAR exists then VALUE is appended to it. If not, VAR is created with VALUE. Thus, it permits to set extra PATH to GNAT compiler and builder folders or GPR\_PROJECT\_PATH. If a line begins with '#' then it is not considered. An example file of gnatstudio\_launcher.rc is provided in the archive. Modify the content and put it in your .gnatstudio folder.

See readme for details.

Limitation: Ada Language Server has some latencies and doesn't respond when parsing source code with more than 1000 lines. It may be due to some compilation options I missed.

There could be some other limitations that you might meet.

Feel free to report them here.

Any help will be really appreciated to fix these limitations.

### KDF9 Pascal, Thanks to Ada

*From: Moi <findlaybill@blueyonder.co.uk>

Subject: KDF9 Pascal, thanks to Ada

Date: Tue, 2 Jul 2024 01:27:43 +0100

Newsgroups: comp.lang.ada*

Some time ago it occurred to me that the best way to illustrate the remarkable architecture of the EE KDF9 would be to write a cross-compiler that generates idiomatic KDF9 Usercode (assembly language) and displays it in association with the source code.

I chose Pascal as the source language, having compiler texts available for retargeting.

PASKAL, which implements a large subset of Pascal, is now available.

The only parts of Pascal not implemented are file types and packed types, including the 'text' type, which means that there is no Standard Pascal I/O. However, I provide some basic KDF9-oriented output routines as a stopgap. They are more than adequate to show the correct execution of, for example, the Whetstone Benchmark, and many other classic codes, such as Quicksort.

PASKAL is written in Pascal, using the fpc compiler, and in Ada 2012, and is included with V11.2c of ee9, my KDF9 emulator (also in Ada 2012).

Included with it are the following documents:

- \* PASKAL: Users' Guide

- \* PASKAL: Object Program Structure.

- \* PASKAL: Implementation Overview

Compiled binaries are available for:

- \* Apple Silicon Macs

- \* Intel Macs

- \* 64-bit Intel (Debian Bookworm) Linux

- \* 64-bit Raspberry Pi (Debian Bookworm) OS

The Intel Linux binary should run under WSL on MS Windows 10 or 11.

Get your copy here:

<http://www.findlayw.plus.com/KDF9/#PSK>

There is a direct link there to the Users' Guide. It includes an example of a complete Pascal program and the corresponding KDF9 Usercode, should that be the extent of your interest.

### Gnoga's 10th Anniversary - 2.2 Released.

*From: Blady <p.p11@orange.fr>

Subject: Gnoga's 10th anniversary - V2.2

released.

Date: Sun, 8 Sep 2024 18:30:49 +0200

Newsgroups: comp.lang.ada*

Gnoga was born on SourceForge [1] on September 8, 2014.

Gnoga (GNU Omnipotent Gui for Ada) is the multi-platform graphics library created natively in Ada. I immediately liked Gnoga for the coherence and simplicity of these APIs naturally fitting together. The programmer can rely on Ada for his business code and on the multitude of Javascript libraries for the graphical interface.

For 10 years Gnoga has evolved in maturity to fulfill its founding principles:

- providing a framework and associated tools for developing GUI applications using the Ada language, leveraging web technologies for application developers

- developing native applications for desktop and mobile just as easy to create, all using the same code base

- providing better tools means better application quality

- offering the application developer a powerful toolset for secure cloud based computing, mobile apps, desktop apps and web apps the combination not found in any other set of tools in any other language

Gnoga statistics:

- 1031 commits

- 2200 downloads

- 2196 posts on the mailing list

- 56 tickets

You'll find a special Gnoga's wiki anniversary page [2] with some materials and my testimony.

Feel free to post your testimony, your own story with Gnoga.

On this occasion, Gnoga V2.2a has been released [3] and [4], with main changes:

- Added key field to keyboard event

- If present command line options gnoga-host, gnoga-port, gnoga-boot and gnoga-verbose will override host, port, boot file and verbosity programmed in source code (see TIPS).

- Improve logging implementation in a separate package in order to allow user defined logging handlers.

- Add a backslash compatibility mode on the behavior of Escape\_String for SQLite with the one for MySQL.

- Change MYSQL\_Real\_Connect profile to better match with documentation

This version has been tested on macOS 13.6 and GNAT 14.1. Please provide feedback of other environments.

- [1] <https://sourceforge.net/p/gnoga/code/ci/45c76779e7af7b869deacc698478eb3ef25cfe91>

- [2] <https://sourceforge.net/p/gnoga/wiki/Gnoga-Anniversary>

- [3] <https://sourceforge.net/projects/gnoga/files>

- [4] [https://sourceforge.net/p/gnoga/code/ci/dev\\_2.2/tree](https://sourceforge.net/p/gnoga/code/ci/dev_2.2/tree)

## Ada Inside

### Canal+ Crash

*From: Nicolas Paul Colin De Gloucester

<master\_fontaine\_is\_dishonest

@strand\_in\_london.gov.uk>*

*Subject: Canal+ crash*

*Date: Fri, 19 Jul 2024 23:41:44 +0200*

*Newsgroups: fr.comp.lang.ada,

comp.lang.ada*

Canal+ uses Ada but one is alleging that Canal+ suffered a crash today with Windows. Cf.

<https://www.UniversFreeBox.com/article/568957/orange-canal-et-bouygues-telecom-annoncent-a-leurs-abonnes-etre-touches-par-la-panne-informatique-mondiale>

Cf. a complaint by Mister Brukardt that Ada cannot control non-Ada software on a shared system.

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Sat, 20 Jul 2024 09:23:11 +0200*

It is not about Ada. It is about the fundamental principle that security cannot be added on top of an insecure system. The lesson never learned is that security levels impose safety problems not solving security issues. Modern security architectures are nothing but a huge scam.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Sat, 20 Jul 2024 07:43:18 -0000*

> It is about the fundamental principle that security cannot be added on top of an insecure system.

Actually, it can. Notice how the Internet itself is horribly insecure, yet we are capable of running secure applications and protocols on top of it.

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Sat, 20 Jul 2024 11:08:47 +0200*

> we are capable of running secure applications and protocols on top of it.

Of course we can. That is the whole idea of the scam. Why on earth do we need security updates? Do you update your screwdriver each week?

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Sun, 21 Jul 2024 01:04:44 -0000*

> Why on earth do we need security updates?

Because computer systems are complex, and new bugs keep being discovered all the time.

> Do you update your screwdriver each week?

I don't depend on my screwdriver to keep my bank account secure.

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Sun, 21 Jul 2024 09:22:06 +0200*

> Because computer systems are complex, and new bugs keep being discovered all the time.

This does not make sense. You can create a very complex system out of screwdrivers and still each screwdriver would require no update.

Systems consist of computers and computers of software modules. There is nothing inherently complex about making a module safe and bug free. Security interactions are primitive and 100% functional. There are no difficult issues with non-functional stuff like real-time problems. It is purely algorithmic while all mathematical complexity of cryptography is NOT what gets updated. It is complex only because it was designed as a Wood Block Tumbling Game.

> I don't depend on my screwdriver to keep my bank account secure.

I don't need a bank account to fasten the screws. Application area is irrelevant.

*From: Niklas Holsti

<niklas.holsti@tidorum.invalid>

Date: Sun, 21 Jul 2024 11:00:36 +0300*

> Security interactions are primitive and 100% functional. There is no difficult issues with non-functional stuff like real-time problems.

Well, several recent attacks use variations in execution timing as a side-channel to exfiltrate secrets such as crypto keys. The crypto code can be functionally perfect and bug-free, but it may still be open to attack by such methods.

But certainly, most attacks on SW have used functional bugs such as buffer overflows.

*From: J-P. Rosen <rosen@adalog.fr>

Date: Sun, 21 Jul 2024 11:10:06 +0200*

> But certainly, most attacks on SW have used functional bugs such as buffer overflows.

A problem that has been solved since 1983, and even before (Pascal had bounds checking). Sigh...

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Sun, 21 Jul 2024 11:19:30 +0200*

> Well, several recent attacks use variations in execution timing as a side-channel to exfiltrate secrets such as crypto keys.

It is always a tradeoff between the value of the information and costs of breaking the protection. I doubt that timing attack are much more feasible in that respect than brute force.

> But certainly, most attacks on SW have used functional bugs such as buffer overflows.

Exactly. Non-functional attacks are hypothetical at best. They rely on internal knowledge which is another problem. An insider work is the most common case of all breaches. So, maybe, it is better to update the staff? (-:)

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Sun, 21 Jul 2024 11:34:14 +0200*

> A problem that has been solved since 1983, and even before (Pascal had bounds checking). Sigh...

Yup, however some crackpot could always suggest an attack on bounds checking, e.g. exception vs. not, index to bounds comparison dependent on the actual values etc., and then produce a lengthy paper on a constructed absolutely unrealistic scenario... (-:)

*From: Niklas Holsti

<niklas.holsti@tidorum.invalid>

Date: Sun, 21 Jul 2024 14:31:27 +0300*

> I doubt that timing attack are much more feasible in that respect than brute force.

Security researchers and crypto implementers seem to take timing attacks quite seriously, putting a lot of effort into making the crucial crypto steps run in constant time.

> Non-functional attacks are hypothetical at best. They rely on internal knowledge which is another problem.

As I understand it, the "internal knowledge" needed for timing attacks is mostly what is easily discoverable from the open source-code of the SW that is attacked.

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Sun, 21 Jul 2024 18:49:27 +0200*

> Security researchers and crypto implementers seem to take timing attacks quite seriously

Cynically: they certainly know how to butter their bread...

> the "internal knowledge" needed for timing attacks is mostly what is easily discoverable from the open source-code

Considering many many layers of software to predict timing from code in uncontrolled environment would be a challenge.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Sun, 21 Jul 2024 21:52:58 -0000*

> You can create a very complex system out of screwdrivers and still each screwdriver would require no update.

There is an old engineering adage, that the complexity of a system arises, not so much from the number of individual components, as from the number of potential interactions between them.

If you have a box full of screwdrivers, then all you have is a box full of screwdrivers.

If you have a computer system made up of a bunch of modules interacting with each other, then you could have, potentially, quite a complex system indeed.

Look up the term "combinatorial explosion" to learn more.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Sun, 21 Jul 2024 21:53:46 -0000*

> A problem that has been solved since 1983, and even before (Pascal had bounds checking). Sigh...

Pascal had no checking for memory leaks or double-frees.

Rust certainly seems to be a next-generation solution to these sorts of memory problems.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Sun, 21 Jul 2024 21:55:10 -0000*

> Considering many many layers of software to predict timing from code in uncontrolled environment would be a challenge.

And yet it has been successfully done on the hardware itself, right down under all those layers of software (cf Spectre/Meltdown).

*From: J.-P. Rosen <rosen@adalog.fr>

Date: Mon, 22 Jul 2024 08:36:08 +0200*

> Pascal had no checking for memory leaks or double-frees.

> Rust certainly seems to be a next-generation solution to these sorts of memory problems.

We were talking about bounds checking, that Pascal had. Nowadays, you should not use pointers directly, but containers. Pointers are necessary only for writing containers, thanks to Ada's features not found in other languages, like allocating dynamically sized arrays on the stack.

Note that in Rust, containers are written using unsafe Rust, therefore Rust is not better than Ada on that aspect, it is a complicated solution to a problem that Ada doesn't have.

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Mon, 22 Jul 2024 09:16:09 +0200*

> If you have a computer system made up of a bunch of modules interacting with each other, then you could have, potentially, quite a complex system indeed.

Tight coupling = bad design. No difference to screwdrivers. However you can take integer arithmetic if you dislike screwdrivers. However complex system you build, there is no need to update integers.

> Look up the term "combinatorial explosion" to learn more.

Bad design leads to explosion of non-trivial unanticipated system states making it unpredictable. This is what happens when you add security on top. You patch holes drilling new ones to fix the patches.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Tue, 23 Jul 2024 01:48:12 -0000*

> We were talking about bounds checking, that Pascal had.

Which is only one potential pitfall for bugs with security implications.

## Ada and Other Languages

### "Red" and the DoD Language Competition

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Subject: "Red" And The DoD Language Competition

Date: Fri, 6 Sep 2024 01:55:00 -0000

Newsgroups: comp.lang.ada*

While browsing around for Ada-related docs some years ago, I came across this site:

<https://iment.com/maida/computer/redref/index.htm>

which collects info on the DoD's "Strawman", "Woodenman", "Tinman", "Ironman" and "Steelman" series of RFPs, and the specs for the "Red" language that didn't become Ada.

*From: Luke A. Guest

<laguest@archeia.com>

Date: Sat, 7 Sep 2024 17:43:26 +0100*

We have all the colours now:

[https://www.reddit.com/r/ada/comments/165f5zg/common\\_hol\\_phase\\_1\\_reports/](https://www.reddit.com/r/ada/comments/165f5zg/common_hol_phase_1_reports/)

## Ada Practice

### Accessing the Command Line

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Subject: Accessing The Command Line

Date: Thu, 4 Jul 2024 00:08:56 -0000

Newsgroups: comp.lang.ada*

```

with Ada.Command_Line;

with Ada.Text_IO;

procedure Echo is

package cli renames

Ada.Command_Line;

package tio renames Ada.Text_IO;

package int_io is new tio.Integer_IO

(Num => Integer);

begin

tio.put("my name: ");

tio.put(cli.Command_name);

tio.Put_Line("");

tio.Put("nr args: ");

int_io.Put(cli.Argument_Count, width => 1);

tio.Put_Line("");

for i in 1 .. cli.Argument_Count loop

tio.put("[");

int_io.put(i, width => 1);

tio.put(": ");

tio.put(cli.argument(i));

tio.put_line("");

end loop;

end Echo;

```

Comments:

Ada, like Python, offers the convenience of being able to specify local "nicknames"

for imported packages, to save some typing.

Having become used to the convenience of printf-style formatting in C and other languages that have adopted it (including Lisp and Python), I don't miss the tedium of having to format and output one item at a time. Though I recognize that there is no way to do printf style in a type-safe fashion, short of going to a fully-dynamic language.

Being able to access the POSIX command line via some globally-defined entity instead of arguments to a "mainline" procedure is something that just about every decent language offers. C is notably absent from this list.

*From: Paul Rubin

<no.email@nospam.invalid>

Date: Wed, 03 Jul 2024 18:16:01 -0700*

> Though I recognize that there is no way to do printf style in a type-safe fashion, short of going to a fully-dynamic language.

C++ does that polymorphism stuff in iostream so you'd write std::cout << "my name: " << command\_line << ...

Haskell does something sort of similar with additional machinery.

printf for some people is one of the motivations for dependent types.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Thu, 04 Jul 2024 01:50:59 -0000*

> C++ does that polymorphism stuff in iostream so you'd write std::cout << "my name: " << command\_line << ...

I know. The disadvantage of the C++ scheme is you cannot easily reorder items as necessary to fit the grammar of localized messages. That, I think, is why lots of other languages (including Python and Lisp) have copied the printf scheme, yet none have seen fit to copy the C++ scheme.

> printf for some people is one of the motivations for dependent types.

I wonder how you would express such a thing in an Ada-friendly fashion?

*From: Jeffrey R. Carter

<spam.jrcarter.not@spam.acm.org.not>

Date: Thu, 04 Jul 2024 13:27:05 +0200*

Remember that you can concatenate strings:

> tio.put("my name: ");

> tio.put(cli.Command\_name);

> tio.Put\_Line("");

Tio.Put\_Line (Item => "my name: " & Cli.Command\_Name);

Image functions thus allow similar simplifications. Image is one such

function, if you can accept the initial space for non-negative values:

```

> tio.Put("nr args: ");

> int_io.Put(cli.Argument_Count,

width => 1);

> tio.Put_Line("");

Tio.Put_Line (Item => "nr args: " &

Cli.Argument_Count'Image);

```

For simple cases you can roll your own:

```

function Image (Value : in Integer) return

String is

Raw : constant String := Value'Image;

begin -- /Image

return Raw (if Value < 0 then 1 else 2) ..

Raw'Last);

end Image;

```

> tio.put("[");

> int\_io.put(i, width => 1);

> tio.put(":");

> tio.put(cli.argument(i));

> tio.put\_line("");

Tio.Put\_Line (Item => "[" & Image (I) & "]:" &

Image (Cli.Argument (I)) );

For more complex uses, you can use something like PragmARC.Images[.Image]

(<https://github.com/jrcarter/PragmARC>).

You probably should review the definition of Ada.Text\_IO

([http://www.ada-auth.org/standards/aarm12\\_w\\_tc1/html/AA-A-10.html](http://www.ada-auth.org/standards/aarm12_w_tc1/html/AA-A-10.html)), especially

for procedure New\_Line.

*From: Dmitry A. Kazakov

<mailbox@dmitry-kazakov.de>

Date: Thu, 04 Jul 2024 15:01:05 +0200*

> with Ada.Command\_Line;

> with Ada.Text\_IO;

[...]

A general advice processing strings, any strings: messages, commands, payload etc.

Always read a complete string into a fixed size buffer (safety). Never use streams. Process the whole string consequently. Never tokenize. Never copy anything. Ada has slices.

The same is true for the output. Build a complete substring in a buffer. Consequently. Flush the complete substring to the output.

Do not use Unbounded\_String.

*From: Rod Kay <rodakay5@gmail.com>

Date: Fri, 05 Jul 2024 01:13:36 +1000*

> I wonder how you would express such a thing in an Ada-friendly fashion?

There is the 'GNAT.Formatted\_String' package, which provides printf functionality.

Unfortunately, its formatting is somewhat buggy and has been so for many years. Usage is quite simple and reasonably elegant but the occasional incorrect formatting is a major problem, essentially rendering the package useless.

There is also the new 2022 f'X = {An\_X\_Variable} notation for embedding Variable'Image into strings, which is very nice. However, it does not allow for formatting, so not useful for your needs. Just thought I'd mention it, as it is now available in GCC 14.

*From: Dmitry A. Kazakov*

*<mailbox@dmitry-kazakov.de>*

*Date: Thu, 04 Jul 2024 18:15:54 +0200*

>> printf for some people is one of the motivations for dependent types.

> I wonder how you would express such a thing in an Ada-friendly fashion?

For example:

[http://www.dmitry-kazakov.de/ada/strings\\_edit.htm](http://www.dmitry-kazakov.de/ada/strings_edit.htm)

*From: Ben Bacaisse <ben@bsb.me.uk>*

*Date: Thu, 04 Jul 2024 20:42:00 +0100*

> ... Though I recognize that there is no way to do printf style in a type-safe fashion, short of going to a fully-dynamic language.

Not so. Haskell has Text.Printf.

*From: Paul Rubin*

*<no.email@nospam.invalid>*

*Date: Thu, 04 Jul 2024 15:06:00 -0700*

> Not so. Haskell has Text.Printf.

Text.Printf is not fully type safe. printf "%d\n" "foo" throws a "bad formatting character" exception, really amounting to a runtime type exception.

*From: Lawrence D'Oliveiro*

*<ldo@nz.invalid>*

*Date: Thu, 04 Jul 2024 23:54:49 -0000*

> Remember that you can concatenate strings:

> Tio.Put\_Line (Item => "my name: " & Cli.Command\_Name);

I'm sure I can, but I'm not sure what the point is. Let Ada collect the pieces in its own buffers. That saves copying steps.

> PragmARC.Images[.Image]

(<https://github.com/jrcarter/PragmARC>).

I don't really feel the need to resort to third-party libraries just to do simple I/O.

*From: J-P. Rosen <rosen@adalog.fr>*

*Date: Fri, 05 Jul 2024 10:58:00 +0200*

> I'm sure I can, but I'm not sure what the point is. Let Ada collect the pieces in its own buffers. That saves copying steps.

Agreed. I don't understand why people dislike printing piece by piece. In the old FORTRAN, you could write only line by line, but this time is long gone...

With the various Put procedures, you have individual formatting options that you don't have otherwise. Moreover, there is a nice property that few people noticed: if you have an algorithm writing data to a file, with loops and so on, you can keep the exact same structure replacing every Put with the matching Get, and you will read your data correctly. This feature goes away as soon as you have a 'Image.

## Reduction Expressions

*From: Simon Wright

<simon@pushface.org>

Subject: Reduction expressions

Date: Tue, 13 Aug 2024 13:36:54 +0100

Newsgroups: comp.lang.ada*

Are the Accum\_Type & Value\_Type (ARM 4.5.10(9/5)) of a reduction attribute reference required to be definite?

ARM 4.5.10(24/5) & (25.5) seem to imply so, which explains why GNAT doesn't support e.g. String.

*From: Randy Brukardt

<randy@rrsoftware.com>

Date: Mon, 19 Aug 2024 22:59:04 -0500*

Accum\_Subtype (we changed the name since it is a subtype, not a type; various clarifications were made to the wording as well in AI22-0011-1, AI22-0047-1, and AI22-0069-1) most likely has to be definite since the accumulator is of that type, and the bounds/constraints of the accumulator are thus defined by the initial value. In most uses, the first call on Reduce would then raise Constraint\_Error (because the bounds/constraints are incorrect). I don't think there is any reason that the Value\_Subtype has to be definite for a sequential reduce (a parallel reduce requires the two subtypes to statically match).

Note that if someone has a clever way to use an indefinite result, it is allowed. For instance, I could see a class-wide result making sense in some limited circumstances. But I don't think String would do anything useful, since the bounds are determined by the initial value.

BTW, this answer is essentially topic #1 of AI22-0011-1.

*From: Simon Wright

<simon@pushface.org>

Date: Tue, 20 Aug 2024 22:23:27 +0100

> Accum\_Subtype (we changed the name since it is a subtype, not a type;*

Amazing how a person (I) can have used Ada for ~40 years and still be hard put to it to describe the difference, at least in a case like this one, where the ARG

members clearly see meanings that leave me lukewarm if not cold. Maybe "the heart of twilight"?

> But I don't think String would do anything useful

String was just the simplest indefinite type for an example.

> BTW, this answer is essentially topic #1 of AI22-0011-1.

Thanks for the pointer.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Tue, 20 Aug 2024 23:30:54 -0000*

> Amazing how a person (I) can have used Ada for ~40 years and still be hard put to it to describe the difference

I thought the difference was obvious. "subtype" is the C equivalent of "typedef", just giving a new name to an existing type. So

**subtype A is B;**

(where A and B are simple identifiers) is valid, whereas

**type A is B;**

is not: a "type" declaration always creates a new type: you have to write at least

**type A is new B;**

and now you have two types with different names that are structurally the same, but not compatible.

*From: Keith Thompson

<keith.s.thompson+u@gmail.com>

Date: Tue, 20 Aug 2024 16:41:55 -0700*

> I thought the difference was obvious. "subtype" is the C equivalent of "typedef" [...]

A subtype with no added constraint is similar to a C typedef, but given

**subtype Digit is Integer range 0..9;**

Digit is distinct from Integer (though they're both the same type).

C doesn't have anything directly corresponding to Ada subtypes.

*From: Lawrence D'Oliveiro

<ldo@nz.invalid>

Date: Wed, 21 Aug 2024 01:37:22 -0000*

> Digit is distinct from Integer (though they're both the same type).

"Integer range 0..9" is a subtype of Integer, and is valid for example as a return type where Integer is expected. The "subtype" declaration doesn't actually create the subtype: "Digit" is just a shorthand name for that, just like a C typedef.

*From: Simon Wright

<simon@pushface.org>

Date: Wed, 21 Aug 2024 08:47:49 +0100

> I thought the difference was obvious.

[...]*

Yes, I've understood that for a long time but ... ARM22 4.5.10(8,9)[1] say

(8) The expected type for a reduction\_attribute\_reference shall be a single nonlimited type.

(9) In the remainder of this subclause, we will refer to nonlimited subtypes Value\_Type and Accum\_Type of a reduction\_attribute\_reference. ...

and in AI 22-0011-1 [2] starting at 22-Oct-2021 5:25 PM,

\* SB: raises a series of observations,

\* STT: "... You really need to think of Accum\_Type as a particular \*subtype\*"

\* SB: "Ok, I was confused - Accum\_Type is a subtype, not a type. So a lot of my message was noise."

If SB can be confused, so can I!

[1] <http://www.ada-auth.org/standards/22rm/html/RM-4-5-10.html#p8>

[2] <http://www.ada-auth.org/cgi-bin/cvsweb.cgi/ai22s/ai22-0011-1.txt?rev=1.2>

*From: Randy Brukardt

<randy@rrsoftware.com>

Date: Fri, 23 Aug 2024 23:27:48 -0500*

> If SB can be confused, so can I!

Which is why we changed the name - if SB can be confused, it is a good bet that there is something wrong with the wording. That's why I usually recommend bleeding edge users use the bleeding edge RM - no point in rediscovering all of the bugs that we already know about.

Unfortunately, in this case, I'm the only one that has the bleeding edge RM because I haven't finished adding all of the approved AIs to it. This group is some that I've done, which is why the answer to your question was relatively easy to find.

## Ichbiah 2022 Compiler Mode

*From: Kevin Chadwick <kc-usenet@chadwicks.me.uk>

Subject: Ichbiah 2022 compiler mode

Date: Thu, 5 Sep 2024 11:52:37 -0000

Newsgroups: comp.lang.ada*

I guess this is a very subjective question.

A number of Ada users have expressed that they would rather Ada was simpler whilst others desire more features.

I appreciate Ada 83 portability but also like a lot of modern Ada features.

Out of interest. Could anyone help me with what a GNAT or other compiler Ichbiah\_2022\_Mode might look like. Perhaps it might be possible to use pragmas to get an estimated mode of what features he might keep or drop.

I can continue research but currently I do not have the details of his objections to Ada 95 and how those may have continued through to today is perhaps a nuanced question.

What do you think Ichbiah would jettison from Ada 2022? All comments welcome.

*From: Jeffrey R.Carter

<spam.jrcarter.not@spam.acm.org.not>

Date: Thu, 5 Sep 2024 15:40:35 +0200*

> I do not have the details of his objections to Ada 95

Ichbiah's objections to Ada 95 are in <https://web.elastic.org/~fche/mirrors/old-usenet/ada-with-null>

*From: Kevin Chadwick <kc-usenet@chadwicks.me.uk>

Date: Thu, 5 Sep 2024 16:08:01 -0000*

What does this mean?

"elimination of accuracy constraints in subtypes"

*From: Jeffrey R.Carter

<spam.jrcarter.not@spam.acm.org.not>

Date: Thu, 5 Sep 2024 21:24:05 +0200*

> "elimination of accuracy constraints in subtypes"

See ARM-95 J.3

([https://www.adaic.org/resources/add\\_content/standards/95lrm/ARM\\_HTML/RM-J-3.html](https://www.adaic.org/resources/add_content/standards/95lrm/ARM_HTML/RM-J-3.html)),

Reduced Accuracy Subtypes.

*From: Randy Brukardt

<randy@rrsoftware.com>

Date: Thu, 5 Sep 2024 19:03:22 -0500*

> What do you think Ichbiah would jettison from Ada 2022?

My recollection is that he wanted a more complex "class" feature, which IMHO would have made Ada more complex, not simpler.

In any case, I can't guess what Ichbiah would have suggested after 40 years of experience. (He probably would have moved on to some other language anyway, you have to be somewhat resistant to change to stick with a single language for your entire career. I seem to resemble that remark... ;-)

What I can do is suggest what an RLB\_2022 mode would look like, as I did the exercise when we all were cooped up during the early days of the pandemic. My philosophy is that Ada has a lot of combinations of features that cause a lot of implementation trouble, but which are not very useful. So I want to reduce the combinations that cause trouble. I note that every feature is useful for something (else it wouldn't be in Ada in the first place). But some things are not useful enough for the trouble that they cause. Also note that I am not worrying about compatibility with Ada, which is always a problem when updating Ada itself.

Here's some highlights off the top of my head:

(1) Simplify the resolution model; essentially everything resolves like a subprogram. For instance, objects resolve similarly to enumeration literals. This substantially reduces the danger of use clauses (having matching profiles and names is less likely than just matching names), and eliminates the subtle differences between a constant and a function (they should really act the same).

(2) Operator functions have to be primitive for at least one of the types in the profile. (Operators in a generic formal part have a pseudo-primitive requirement.) That includes renamings. In exchange for that, operators have the same visibility as the type (which means they are always directly visible when any object of the type is visible). One then can eliminate "use type" (since it would literally do nothing).

(3) A number of syntax options are eliminated. Matching identifiers are required at the end of subprograms and packages. Initializers are always required ( $\langle\rangle$  can be used if default initialization is needed). Keyword "variable" is needed to declare variables (we do not want the worst option to be the easiest to write, as it is in Ada).

(4) Anonymous types of all sorts are eliminated. For access types, we would use aspects to declare properties (static vs. dynamic accessibility, "closure" types, etc.). For arrays, see next item.

(5) The array model would be greatly simplified. New Ada users (and old ones as well) have a hard time dealing with the fact that the lower bound is not fixed in Ada. Additionally, the existing Ada model is very complex when private types are involved, with operators appearing long after a type is declared. The more complex the model, the more complex the compiler, and that means the more likely that errors occur in the compiler. There also is runtime overhead with these features. The basic idea would be to provide the features of an Ada.Containers.Vector, and no more. Very little is built-in. That means that arrays can only be indexed by integers, but that is a good thing: an array indexed by an enumeration type is really a map, and should use a map interface. So I would add a Discrete\_Map to the Ada.Containers packages.

Bounded\_Arrays are a native type (most of the uses of arrays that I have are really bounded arrays built by hand).

A side-effect of this model change is to greatly simplify what can be written as discriminant-dependent components. Discriminant-dependent arrays as we know them are gone, replaced by a parameterized array object that has only

one part that can change. Much of the nonsense associated with discriminant-dependent components disappears with this model.

(6) Static items have to be declared as such (with a "static" keyword rather than "constant"). Named numbers are replaced by explicit static constants. (I would allow writing Universal\_Integer and Universal\_Real, so one could declare static objects and operations of those types.)

(7) Types and packages have to be declared at library-level. This means that most generic instances also have to be declared at library-level. Subtypes, objects, and subprograms still can be declared at any nesting level. I make this restriction for the following reasons:

(A) Accessibility checks associated with access types are simplified to yes/no questions of library-level or not. The only cases where accessibility checks do any real good is when library-level data structures are constructed out of aliased objects. These would still be allowed, but almost all of the complication would be gone. Even if the check needs to be done dynamically, it is very cheap.

(B) Tagged types declared in nested scopes necessarily require complex dynamic accessibility checks to avoid use of dangling types (that is, an object which exists of a type that does not exist).

(C) Reusability pretty much requires ODTs to be declared in library-level packages. Mandating that won't change much for most programs, and you'll be happier in the long run if you declare the types in library packages in the first place.

(D) There are a lot of semantic complications that occur from allowing packages in subprograms, but this is rarely a useful construct.

(8) Protected types become protected records (that is, a regular record type with the keyword "protected"). Primitive operations of a protected record type are those that are protected actions. (Entries can be declared and renamed as such, they would no longer match procedures, which leads to all kinds of nonsense.) This would eliminate the problems declaring helper types and especially \*hiding\* helper types for protected types. (See the problems we had defining the queues in the Ada.Containers to see the problem.) The protected operations would allow the keyword "protected" in order to make the subprograms involved explicit.

(9) Strings are not arrays! Strings would be provided by dedicated packages, supporting a variety of representations. There would be a Root\_String'Class that encompasses all string types. (So many

operations could be defined on `Root_String'Class`).

(10) Variable-returning functions are introduced. They're pretty similar the semantics of anonymous access returns (or the aliased function returns suggested by Tucker). This means that a variable can easily be treated as a function (and indeed, a variable declaration is just syntactic sugar for such a function).

(11) Various obsolete features like `representation_clauses`, `representation_pragmas`, and the ability to use `'Class` on untagged private types are eliminated or restricted.

There were a couple of areas that I never made up my mind on: